Looking for some feedback on PCB stackups for EMI immunity for a prototype daughter board to extend 4 traces approx. 4 inches from a 10-pin, 0.1" header on an eval board to some plastic-optical-fiber transceivers, each trace running at 50 MHz for TI’s Fast Serial Interface out of their C2000 MCU line. The fiber transceivers are sitting right next to VFD power electronics so EMI hardening is high on my list of things to look out for.

Rough daughter board specs so far:

- Sit atop a TI LaunchPad-XL F280025C evaluation board (LAUNCHXL-F280025C Development kit | TI.com) and connect to the 10-pin FSI (Fast Serial Interface) header.

- Route TX-CLK and TX-DATA to two Broadcom AFBR-1629Z DC-50 Mbaud transmitters. Route RX-CLK and RX-DATA to two Broadcom AFBR-2529Z receivers. CLK/DATA pair should have minimal skew, TX and RX channels are independent so all four lines don’t necessarily have to be matched length but will probably try my best anyway.

- 2"x3.5" outside dimensions to reach from the FSI header and have the fiber transceivers sit over the LaunchPad’s USB port.

I’ve used this 4-layer stackup for a few boards but mostly for signals <100 kHz

Signal/Ground/PWR/Signal

I came across this article and their idea for 6-layer GND/Signal/PWR/GND/Signal/GND seemed like the overkill I’m looking for.

It looks like the cost of 6-layer on JLCPCB, even with their impedance control option, is still in the budget. Is this overkill or am I on the right track here?

Here’s what I have so far in Eagle:

GND/Signal/PWR/GND/Signal/GND

100mil curved radius miters

yellow traces are layer 2

orange traces are layer 5

trace lengths are all within 0.01mil using the Meander tool (not sure what the LaunchPad eval board does for its traces on the other side of the FSI header but I’m guessing this is as good as I can do?)

Trace with right now is 9mils for OSHPark’s 6-layer thicknesses calculated with Saturn PCB Design’s stripline-asymmetric tool to get to a 49.276 ohm trace, not exactly sure what I need for this.

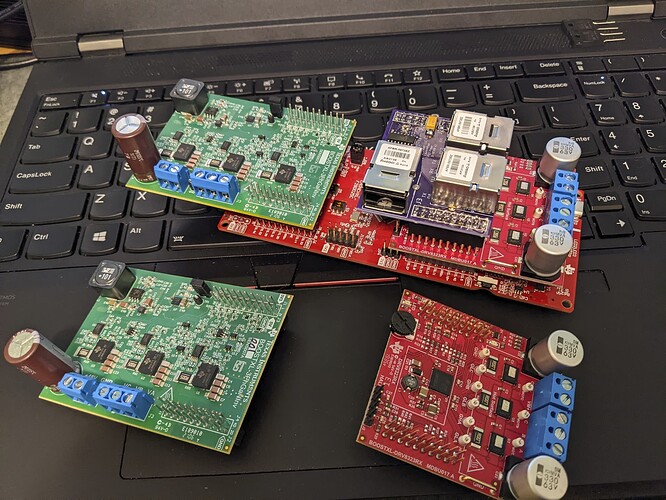

LaunchPad eval board with some more eval daughter boards

LaunchPad is on the bottom

Green daughter card is a TI 3-phase bridge eval board

Red board with the two aluminum polymer caps is another 3-phase bridge eval board

Purple OSHPark board is a first go at an FSI board using Broadcom HFBR-5972 plastic fiber transceivers, pretty cool with LVDS inputs, but FSI turns out to be a burst message, not continuous, so the HFBR-5972’s complained since they’re expecting 8b/10b encoding with no dc bias in the signal or they go into sleep mode.

This new board will be to replace the purple board with the DC-50 Mbaud transceivers which will be friendly to the burst FSI messages.

For some more background,

I’m working up to a test using the TI C2000 series MCU LaunchPad-XL F280025C to try out their Fast Serial Interface (FSI) which is rated for 100Mbit in a daisy-chained network topology. The TX/RX CLK runs at up to 50 MHz and the TX/RX DATA lines are 50 MHz double-data-rate to get 100 Mbit. I’m only going to use one of the two data lines.

.

App note on their daisy-chaining for power converter applications:

The application really needs fiber isolated signaling otherwise TI’s approach using the Cat5 cables with LVDS would be ok. I’m getting more practice with Eagle’s meander tool for trace length matching, this higher